淺析專用集成電路與集成電路設(shè)計(jì)

專用集成電路(Application-Specific Integrated Circuit,簡稱ASIC)是現(xiàn)代電子系統(tǒng)的核心組成部分。與通用集成電路(如CPU、GPU)不同,ASIC是為特定應(yīng)用或特定客戶需求而專門設(shè)計(jì)、制造的集成電路。這意味著其功能在制造時已被固定,無法通過軟件更改,但也因此能在其預(yù)設(shè)任務(wù)上實(shí)現(xiàn)極高的性能、能效和成本效益。

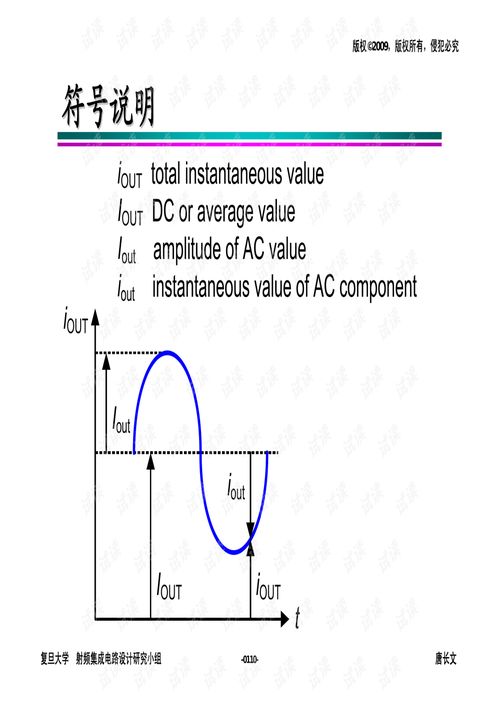

集成電路設(shè)計(jì)則是將抽象的電路功能描述,通過一系列復(fù)雜而精密的流程,轉(zhuǎn)化為可在硅片上制造的物理版圖的過程。這個過程通常分為前端設(shè)計(jì)和后端設(shè)計(jì)兩大階段。前端設(shè)計(jì)主要包括系統(tǒng)架構(gòu)設(shè)計(jì)、寄存器傳輸級(RTL)代碼編寫(使用硬件描述語言如Verilog或VHDL)、功能仿真驗(yàn)證以及邏輯綜合。后端設(shè)計(jì)則專注于將綜合后的網(wǎng)表轉(zhuǎn)化為具體的物理版圖,涉及布局規(guī)劃、時鐘樹綜合、布線、物理驗(yàn)證等一系列步驟,以確保最終設(shè)計(jì)滿足時序、功耗和制造工藝的要求。

專用集成電路的設(shè)計(jì)正是集成電路設(shè)計(jì)領(lǐng)域中最具挑戰(zhàn)性和定制性的分支之一。一個典型的ASIC設(shè)計(jì)流程始于明確的市場需求或系統(tǒng)規(guī)格,設(shè)計(jì)團(tuán)隊(duì)需要深入理解應(yīng)用場景,權(quán)衡性能、功耗、成本、開發(fā)周期等多重因素,進(jìn)行架構(gòu)探索。例如,用于比特幣挖礦的ASIC追求極致的哈希計(jì)算效率,而用于智能手機(jī)射頻前端的ASIC則可能更注重功耗與信號完整性。

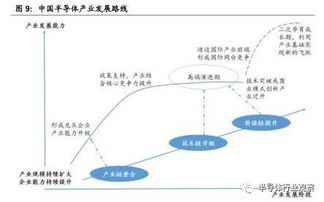

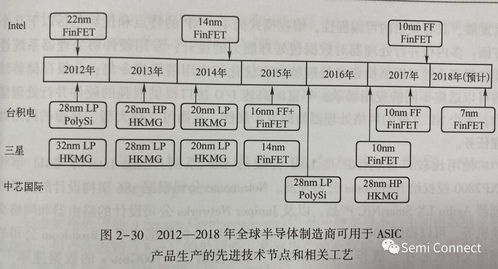

隨著工藝節(jié)點(diǎn)不斷微縮(如進(jìn)入5納米、3納米時代),ASIC設(shè)計(jì)面臨的挑戰(zhàn)也日益增多,包括設(shè)計(jì)復(fù)雜度呈指數(shù)增長、功耗與散熱問題、信號完整性與可靠性、以及高昂的制造成本和流片風(fēng)險(xiǎn)。因此,現(xiàn)代ASIC設(shè)計(jì)高度依賴電子設(shè)計(jì)自動化(EDA)工具鏈,并廣泛采用基于已驗(yàn)證IP核的設(shè)計(jì)方法,以提升設(shè)計(jì)效率和成功率。

總而言之,專用集成電路以其無可替代的定制化優(yōu)勢,深度賦能從數(shù)據(jù)中心、人工智能、通信設(shè)備到消費(fèi)電子等眾多領(lǐng)域。而不斷演進(jìn)的集成電路設(shè)計(jì)方法論與工具,正是將創(chuàng)新構(gòu)想轉(zhuǎn)化為強(qiáng)大“硅基石”的關(guān)鍵橋梁,持續(xù)推動著信息技術(shù)的飛速發(fā)展。

如若轉(zhuǎn)載,請注明出處:http://www.xinntv.cn/product/90.html

更新時間:2026-04-11 02:00:35